## USING CHARM<sup>®</sup>-2 TO QUANTIFY WAFER CHARGING IN ION AND PLASMA-BASED IC PROCESSING EQUIPMENT

Wafer Charging Monitors, Inc. 127 Marine Road Woodside, California 94062

tel. 650-851-9313 fax. 650-851-2252 e-mail: sales@charm-2.com web site: www.charm-2.com

This introduction to CHARM-2 charging monitors is intended to briefly explain the basics of CHARM-2 wafers, and to illustrate some applications possible with the use of CHARM-2 charging monitors.

This presentation is **not** a complete survey of all possible applications. If you have questions about applications not included here, please contact Wafer Charging Monitors. It is very likely that we have experience with them, as well.

CHARM-2 wafers are very easy to use. Just put them in the process chamber and run the process (or an abbreviated process). The CHARM-2 wafers are then tested on a parametrict tester to read out the stored data. Following this, they are re-programmed on a parametric tester to erase the stored data, and they are ready for the next application.

The parametric test data is processed with PC-based WCM ChargeMap data analysis software to obtain wafer maps of surface-to-substrate potentials, UV intensity, and J-V plots of the equipment charging characteristics.

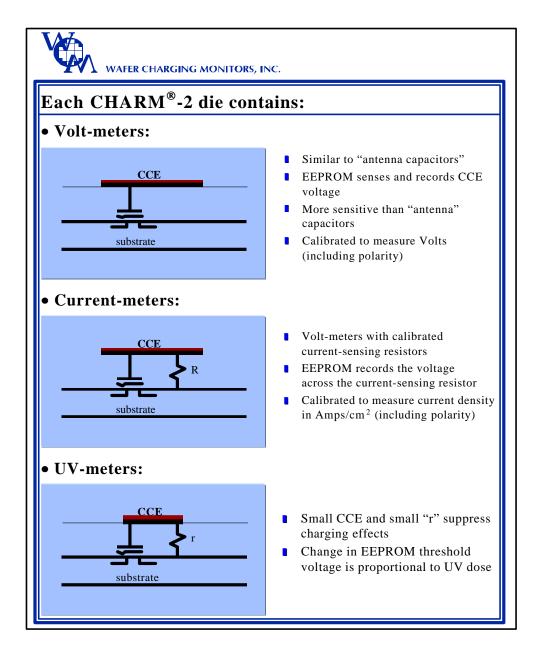

Because CHARM-2 sensors are composed of circuit elements (EEPROM transistors, resistors, and diodes) whose behavior is well-understood and characterized, the response characteristics of the CHARM-2 sensors are fixed by design. Consequently, the interpretation of CHARM-2 results is unambiguous.

Because separate, individually optimized, sensors are used to measure electrostatic charging vs. UV, charging effects and UV effects are never confused. This is particularly important for plasma applications, where the UV intensity is usually very high.

A complete discussion of the principles of operation of the CHARM-2 sensors is contained in WCM Technical Note 1: "The Fundamentals of CHARM-2", available from Wafer Charging Monitors, Inc.

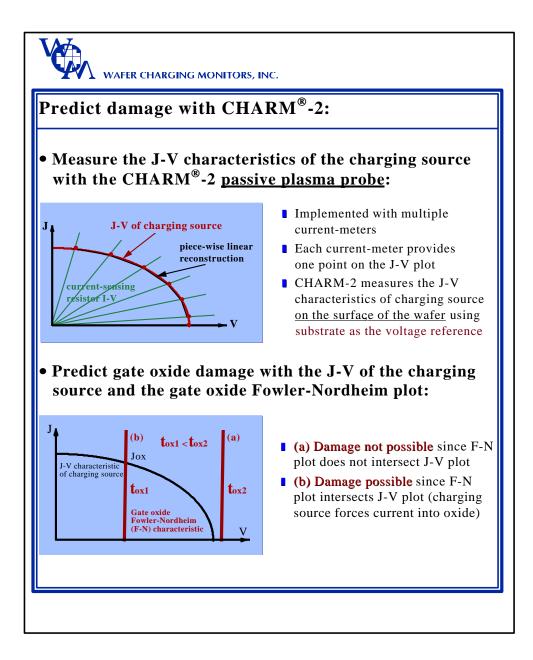

The CHARM-2 passive plasma probe may also be thought of as on-wafer, wireless, Langmuir probe. The important difference between the two is the voltage reference: the Langmuir probe uses the wall of the process chamber, whereas CHARM-2 uses the wafer substrate. Since gate oxide damage is due to voltage difference between the surface of the wafer and the substrate, CHARM-2 J-V plots may be used to predict product damage, where as Langmuir probe plots may not.

Prediction of charging damage using CHARM-2 data is discussed in detail in WCM Technical Note 2: "Understanding CHARM-2 Data and its Relationship to Charging Damage", available from Wafer Charging Monitors, Inc.

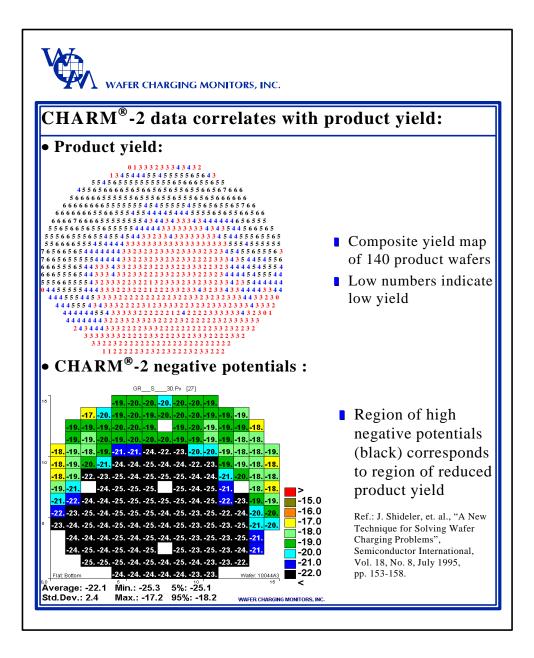

This example shows the spatial correlation between region of reduced yield on 140 EEPROM product wafers and the region of very high negative voltages recorded with the CHARM-2 wafers. (CHARM-2 voltmeters are saturated - the actual values are higher than indicated in the CHARM-2 wafer map.) The region of high negative voltages recorded with the CHARM-2 wafer corresponds to region of significant yield loss on the product wafers.

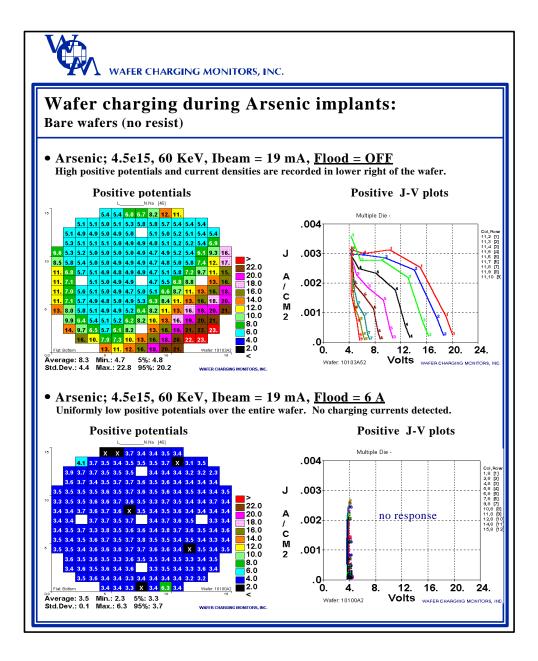

The example at the top of the page shows that high positive potentials are recorded in the lower right of the wafer when the plasma flood system is turned OFF during a high-current Arsenic implant. The J-V graph shows the J-V plots recorded in individual die in column 11. The "1" J-V plot corresponds to die location (x=11, y=2), a region of high positive voltage and very high current density, while the "9" J-V plot corresponds to die location (x=11, y=10), a region of significantly reduced positive charging.

The example at the bottom of the page shows what happens when the plasma flood system is turned ON. The positive potentials are uniformly reduced all over the wafer, and no J-V plots are measured above 4 Volts.

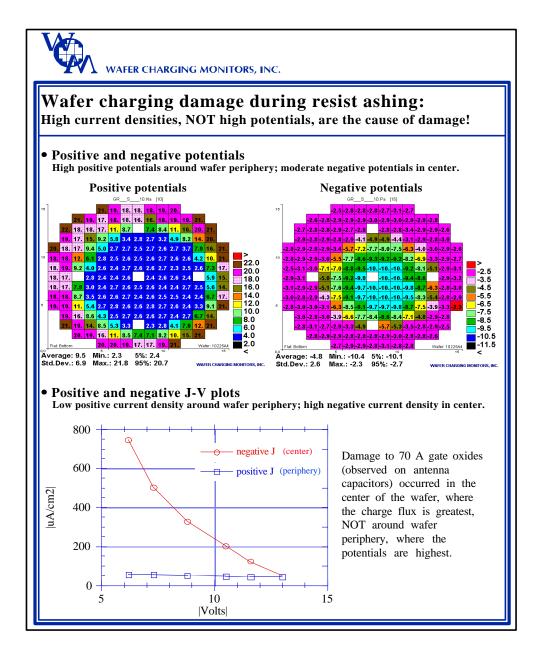

This example illustrates that regions of high potentials are not necessarily the regions of damage, and that regions of lower potentials are not necessarily free of damage. The positive potentials wafer map shows high positive voltages around the periphery of the wafer, while the negative potentials wafer map shows lower negative voltages in the center of the wafer. However, damage to 70 A antenna capacitors was observed in the center of the wafer. This result can be understood when the positive and negative current densities are taken into account. As shown in the graph at the bottom of the page, the negative current density (measured on die in the center of the wafer) is significantly higher than the positive current density (measured on die around the periphery of the wafer) at voltages which would cause charge conduction in 70 A oxides. Consequently, greater damage will be done by the negative currents, in the center of the wafer.

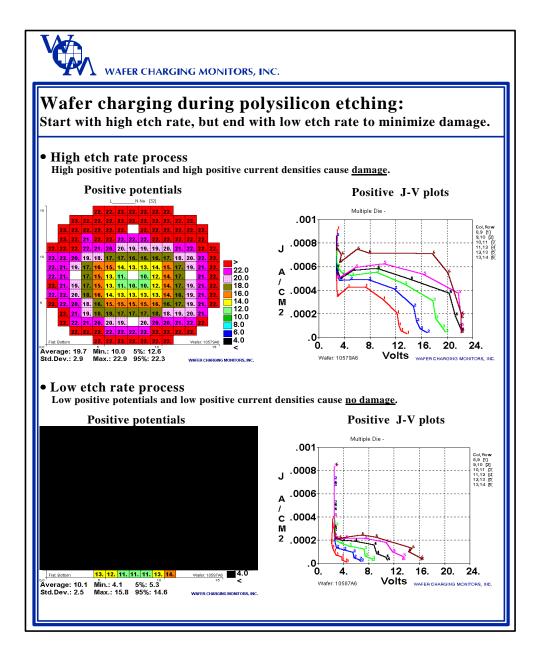

This is an example of process optimization to eliminate charging damage during polysilicon etching. As shown at the top of the page, the high-etch-rate process generates positive potentials which likely exceed 26 V around the periphery of the wafer (as determined from the shape of the positive J-V plots, which are saturated at 22 V). These high potentials are also accompanied by high positive current densities. On the other hand, the low-etch-rate process, shown at the bottom of the page, generates considerably lower potentials and lower current densities. (The four-fold symmetry of the positive potentials is due to four coils around the etching chamber, which are employed to generate the magnetic field used to increase plasma density.)

Since damage occurs after the polysilicon film is separated into individual "islands", the optimized process uses the high-etch-rate process to do most of the etching, followed by the low-etch-rate process to separate the polysilicon film into into individual "islands", and finish the etching. This procedure retains most of the high through-put of the high-etch-rate process, with the low damage of the low-etch-rate process.

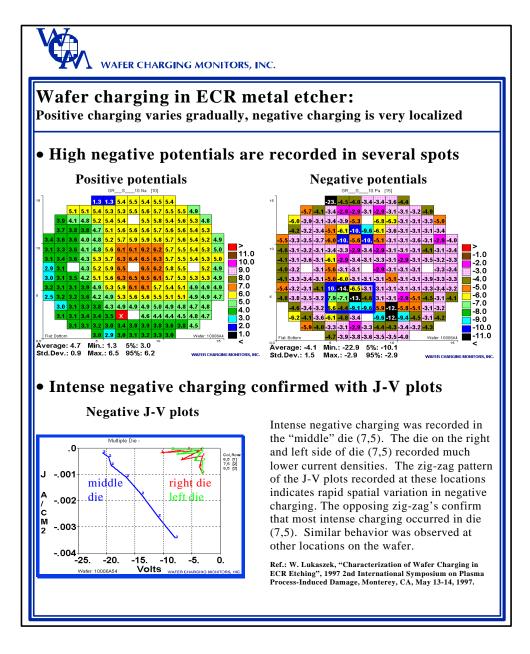

Although the distribution of positive potentials is "well-behaved", the negative potentials wafer map indicates regions of highly localized negative charging. The negative J-V plots confirm this. Sigificant differences in negative potentials were observed on sensors less than 1 mm apart. This indicates that damage monitors used to analyze the charging characteristics of this tool must have high spatial resolution, and the ability to confirm the validity of isolated, anomalous results.

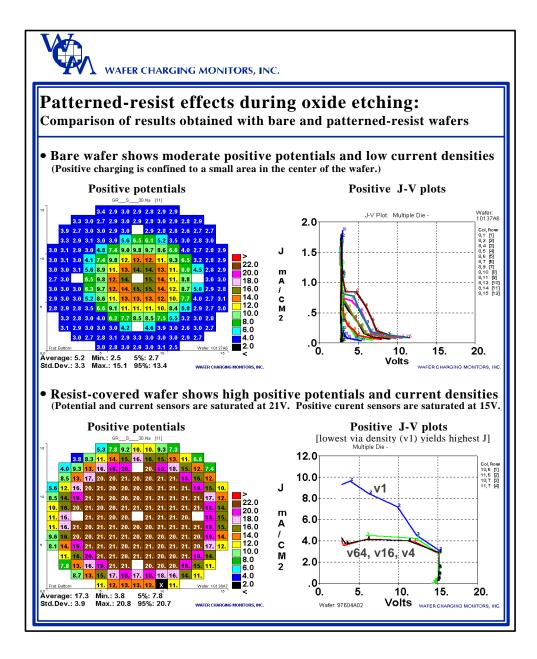

The presence of masked resist on the surface of the wafer can have a significant effect on the charging voltages and currents. The positive potentials and J-V plots measured with a bare CHARM-2 wafer during this oxide etch process are considerably lower than potentials and currents measured when a CHARM-2 wafer is covered with resist patterned with a four-field via mask. (Each field contains different density of vias: field v64 contains the highest density of vias, while field v1 contains the lowest density.) In this tool, the charging current also increases when the via density decreases.

It is also interesting to note that increased positive charging observed here is for 1.5um vias, where enhanced charging due to the "electron shading" effect should be negligible.

Reference: W. Lukaszek, J Shields, and A. Birrell, "Quantifying Via Charging Currents", 1997 2nd International Symposium on Plasma Process-Induced Damage, May 13-14, Monterey, CA.

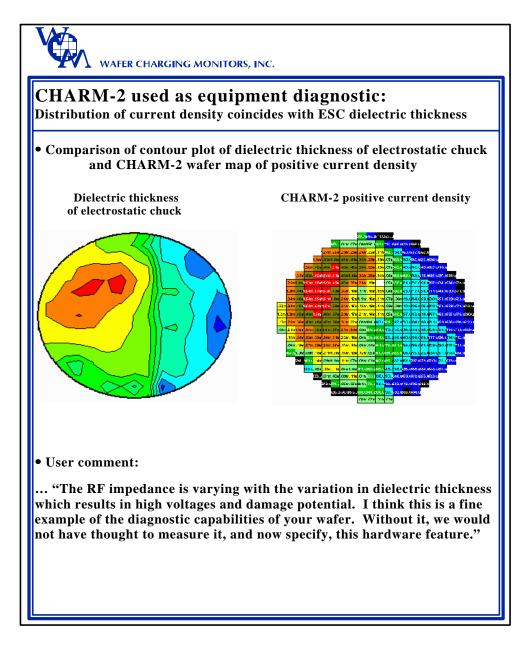

It was proposed that the non-uniform steady-state current distribution observed during the oxide deposition was due to non-uniform RF impedance of the electrostatic chuck. This appears to be the case, since the spatial variation in the thickness of the dielectric on the electrostatic chuck matches the distribution of the steady-state current density measured with the CHARM-2 wafer.